Pick    Important: This paper presents a method for implementing a wideband intermediate frequency digital receiver based on FPGA .

introduction

In modern communication systems, people have proposed a variety of all-digital modulation and demodulation schemes, and the research of all-digital receivers is the key. Among them, orthogonal demodulation technology can realize the extraction of signal phase and amplitude information. Therefore, it is more and more widely used.

Compared with other demodulation methods, the QPSK modulation method has good anti-noise performance, less power spectrum segment occupation, and high data transmission rate, which is a better modulation method. For wideband, high carrier frequency QPSK modulated signals, if the clock is sampled with a clock that is more than twice the highest frequency of the signal, existing devices simply cannot meet the requirements, so undersampling technology must be used to reduce the performance of the system on ADC devices and signal processing devices Claim.

Now large-scale integrated circuit design has grown to the scale of integrating a complex system on one chip, so a single-module, single-chip receiver is not only achievable, but also an inevitable trend. The receiver demodulation function can be realized by software and the high-speed FPGA chip can be used to realize the entire receiver demodulation part with a single chip; by modifying the software, the receiver function can be changed, and because both the software and the hardware are a module, It is convenient to expand functions and connect with other systems, which is also in line with the idea of ​​software radio. Based on the above reasons, a broadband IF digital receiver system implemented by a single-chip FPGA is proposed here .

Picture 1 Â Â IF digital receiver

Â

Picture 2 Â Â NCO structure diagram

Picture 3 Â Â Demodulator software implementation

system structure

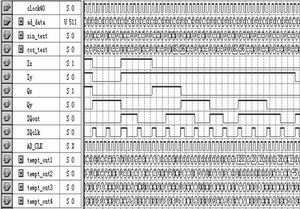

The receiver realizes demodulation of QPSK modulated signals with carrier frequency of 70MHz , data rate of 9.856Mbps , and maximum carrier frequency deviation of ± 80kHz . The received modulated signal passes through AGC and band-pass filter, through high-speed ADC intermediate frequency sampling, digital signal is sent to FPGA to realize demodulation function ( see Figure 1) .

Because the received signal is a high carrier frequency, band-pass signal, it must use undersampling technology. For this system, the signal carrier frequency is 70MHz and the bandwidth is about 10MHz , then

fh = n · B + k · B

Where B is the bandwidth , here 10MHz, n = 7, k = 0.5 According to the sampling theorem, the minimum sampling frequency is:

fs = 2B (1 + k / n)

Approximately equal to 21.4MHz . The selection of sampling frequency should consider two factors: one is to meet the sampling theorem of the band-pass signal, and the spectrum cannot be aliased after sampling; the second is that the data rate after sampling must meet the requirements of post-processing. For the sampling frequency of this system, choose 40MHz , after sampling the signal spectrum will be mirrored to the frequency band with 10MHz as the center bandwidth of 10MHz .

After the A / D conversion, the digital signal directly enters the FPGA to complete the demodulation and extract the modulated data. Due to the all-digital demodulation method, the characteristics of the I and Q digital mixers and filters are completely consistent, avoiding the I and Q channels caused by the unsatisfactory consistency and stability of analog device characteristics during analog demodulation The phenomenon of unbalanced amplitude and large phase quadrature error. For a receiver using coherent demodulation, since the received modulated signal usually has Doppler frequency shift and carrier frequency difference, the performance of demodulation mainly depends on the accuracy of carrier recovery and clock extraction.

The carrier recovery circuit uses a digital COSTAS ring, which combines carrier extraction and demodulation to complete the demodulation function while extracting the carrier. This kind of loop has a rectangular phase detection characteristic, with a small static phase difference and a large lock bandwidth; at the same time, its phase detection characteristic has four phase ambiguities, so it is necessary to add an absolute / relative code conversion circuit during modulation , During demodulation, a relative / absolute code conversion circuit is added to overcome phase ambiguity. The core of the carrier recovery circuit is the generation of the local oscillation source. The digital control oscillation source (NCO) is used to generate the local carrier in the digital circuit. The NCO ( see Figure 2) has a fast frequency agility, a relatively wide bandwidth, and a high frequency resolution Can output two completely orthogonal carrier waves.

The output frequency of NCO is:

fnco = DF · fclk / 2 π = FCW · fclk / 2a

Wherein the frequency control word FCW is, a is a frequency control every word length, fclk is the clock frequency.

Clock extraction ( bit synchronization ) uses a lead - lag digital phase-locked loop circuit. The input phase reference is compared with the phase pulse of the local reference clock n times after frequency division to produce a lead or lag pulse. The symbol synchronization is adjusted under the control circuit The phase of the pulse. The principle of adjustment is that when the reference phase pulse leads the input phase reference, the phase comparator outputs the leading pulse and triggers the deduction gate to subtract one pulse, the phase of the reference phase pulse is pushed back by 1 / n cycle; on the contrary, when the reference phase pulse lags When the phase reference is input, the phase comparator output lag pulse triggers the addition gate to add a pulse, and the phase of the reference phase pulse advances by 1 / n cycle. After repeated phase adjustment, symbol synchronization is achieved, and a bit synchronization clock is generated.

After carrier recovery and clock synchronization are completed, symbol sampling and discrimination, relative code / absolute code conversion, and parallel / serial conversion are performed, and finally, demodulated data is output.

Software receiver and hardware implementation

In modern electronic design, in order to shorten the design cycle, electronic design automation (EDA) has gradually become the key to the success or failure of project design. Quartus  II is the FPGA development platform provided by Altera Corporation . It integrates all the tools required for FPGA development such as editing, simulation, synthesis, and chip programming. Together with other system-level simulation software, it can greatly shorten the system design cycle. FPGA chip adopts Altera 's EP1S10 series, which has rich internal resources and complete external interfaces.

Table 1 shows the main resources occupied by the chip after synthesis .

In the process of software implementation, the most important thing is to correctly and efficiently implement high-speed and complex combinational logic and sequential logic circuits, and use a comprehensive hardware description language program to realize the system functions. Because the demodulation part is all done in FPGA , the whole system only needs one FPGA chip and corresponding configuration chip, A / D converter, analog filter, radio frequency processing circuit plus power supply circuit and signal output interface, the hardware structure is very simple.

System simulation and measured results

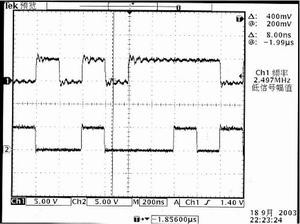

Fig. 4 is the simulation result of the system when the carrier frequency difference is + 20KHz , and Fig. 5 is the demodulation result of the I and Q channels displayed on the oscilloscope during the actual measurement of the system hardware .

Conclusion

After actual hardware testing, each functional module works normally, the receiver fully meets the system design requirements; and the system has a simple structure, low power consumption, and convenient debugging. With the continuous development of large-scale integrated circuit design technology, the generation of high-speed digital signal processors and the application of efficient EDA tools, the modular integration of complex systems will become easier. â–

Picture 4 Â Â System simulation results

Picture 5 Â Â I , Q demodulation measured results

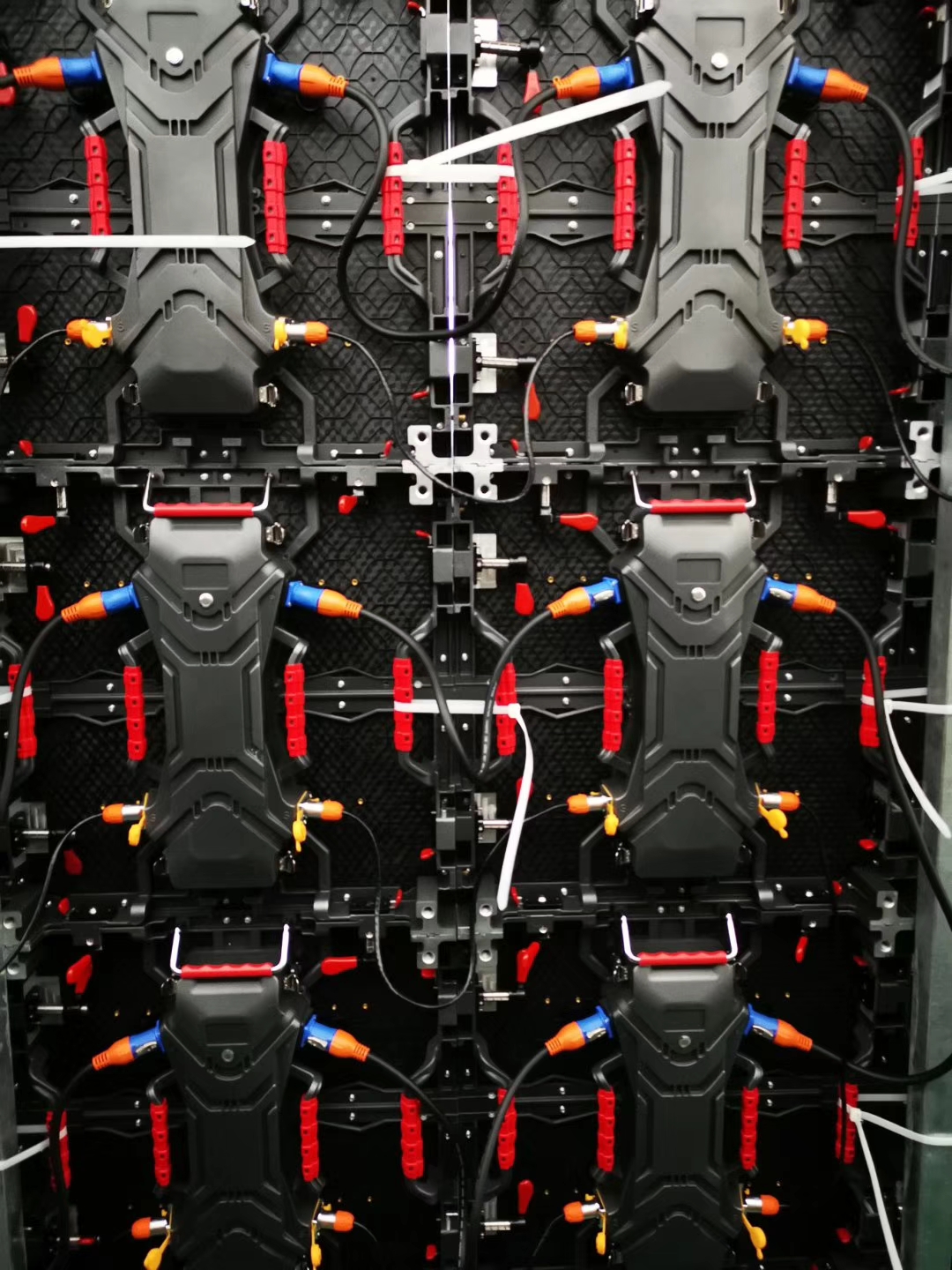

Indoor Rental Led Display Features:

1. LED indoor rental screen is moving towards small spacing and high definition, and small Led Display can show more content;

2. Air insertion and quick lock structure are adopted between screens, which are easy to disassemble and assemble, can be maintained in front and back, and can be transported by air box, fast and safe.

3. The module can be maintained before and after, and the single module can be disassembled for maintenance. When packing, there are positioning posts and strong magnets. There is no seam between modules.

4. The cabinet body is of die-casting aluminum structure, with elegant and beautiful appearance, light and thin weight and hard strength.

5. According to the requirements of the site, the angle can be adjusted inside and outside, inside and outside plus or minus 15 °, splicing into different shapes.

6. All aluminum structure, good heat dissipation, no fan, no noise.

7. The brightness can be adjusted. According to the indoor brightness, adjust the best light effect.

Indoor Mobile LED Display description: compared with the traditional dance scenery and lighting, the display is single and the vision is tired. It is difficult to bring the visual expectation and the enjoyment of the visual beauty to the audience. LED display is very easy to solve these problems. Shocking visual effect, active performance atmosphere, show more video content. The acquisition of these information is far greater than the effect of traditional dance scenery and lighting. The indoor mobile rental screen has developed from the original big spacing pixels p7.62, P6 and P4 to the small spacing pixels p2.976, p3.91 and p4.81. The cabinet size has also developed from the original model to the easy to distinguish and install models of 500m * 500mm and 500mm * 1000mm.

Structure: the box body is made of die-casting aluminum, with internal soft and hard links, external super five types of network cable and aviation plug links, and each box body is equipped with a quick lock.

Precautions: the screen body is often disassembled, and the edges and corners of the screen body are easy to bump. In the process of transportation, disassembly and installation, pay attention to handle with care. In the purchase process, let the manufacturer more with mask, bottom shell and the same batch of LED lights.

LED Wall Rental,Video Wall Rental,LED Screen Rental

Shenzhen Vision Display Technology Co,.LTD , https://www.ledvdi.com